在PCB中接地

1、公共代碼干擾對PCB內部信號的影響

印刷電路板(PCB)內部印刷線具有相對于參考接地板的寄生參數,當功能信號在PCB內傳輸時,電路中同一網絡中的同一等電位節點不再具有等電位。PCB內部的電流i從源端開始,通過一系列載流子返回信號源,形成信號。更重要的是,我傾向于沿著具有低阻抗的路徑流動,因此我通常保持不變的阻抗穩定性。

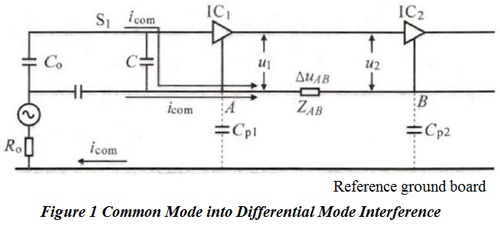

圖1顯示了共模干擾轉換為PCB內差模干擾的過程, 指PCB流內的差模電流而我COM是指共模電流,要么從外部PCB開始,并通過參考接地板流入PCB或PCB,并返回到PCB的內部的內部通過參考地開始板。高頻我COM有兩條路徑:是從點甲到點乙內PCB從GND開始; 第二個是從端口S 1開始從A點到B點到PCB內由電容C.接地阻抗? AB導致Δ的產生ü AB,所以當正常信號被傳遞到IC 2,變形將發生的信號和共模干擾被轉化成差模干擾,從而產生影響基于亦即式正常信號ù 2 = ? 1 -Δ ü AB。

差模干擾的共模

因此,只要我COM進入PCB的內部通過I / O端口或空間輻射,差模濾波器電容在PCB的信號線只能按干擾旁路到GND。該結果的先決條件是GND被認為是信號回流的低阻抗,并且電流總是朝向低阻抗方向流動。

2、電磁兼容EMC設計實施的關鍵:PCB中的接地阻抗

由高頻信號產生EMC的原因在于信號參考電平GND不能保持其低阻抗特性。隨著參考電平阻抗Z GND的增加,信號傳輸質量也會降低。為了解決高頻干擾的問題,在EMC設計中使用了常用的方法,例如與“接地”緊密連接的濾波器,接地和屏蔽。

濾波器可視為對地電容,有兩種結構,一種是將X電容連接到信號參考地,另一種是通過Y電容或PCB內部的不同接地連接使信號連接到金屬殼。屏蔽可以視為PCB地面向太空擴展的結果。濾波器或屏蔽的目的是使高頻共模干擾通過低阻抗旁路,以避免流入正常工作信號。同樣,除非地面具有低阻抗,否則所有這些方法都不起作用。

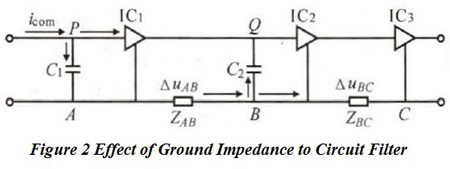

圖2顯示了接地阻抗對電路濾波器的影響

我COM根據IC的順序流1 →IC 2 →IC 1,并且當它流至點P,我COM將流入IC的分支電路1 和c ^ 1 ,通過它從點流到甲到乙。如果A點和B點之間的阻抗,即Z AB,遠小于點P和IC 1之間的阻抗。在這一刻,我COM從點P流向A,可以實現IC 1濾波器。當i com流向B點時,將出現B → C和B → Q的分支電路。如果PCB布局沒有得到很好的控制,點之間的阻抗乙和?,即? BC,? BC >> ? C2 + ? Q。Z Q指的是點Q和IC 2之間的阻抗。一世當最初僅用于IC 2的電容在信號入侵干擾中起作用時,com通過C 2向后流回IC 2輸入端口。

接地阻抗對電路濾波器的影響

為了使參考電平具有低阻抗,通常將其設計為表面,一般而言,長寬比小于5的導體在工程領域可視為低阻抗,印刷線的阻抗不是由其長度或厚度決定的。在傳統的PCB設計原則中,大量推薦模擬電路單點接地,因此數字電路多點接地和數字模塊電路混合接地的PCB布局原則不再適用于處理EMC問題。

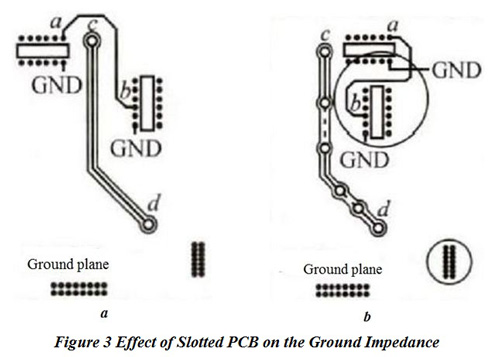

由于必須確保所有信號的所有回流都具有低阻抗的集成接地,因此具有集成接地層的4層或多層板能夠滿足要求,而低成本單板則不能滿足要求,當必須根據成本限制使用雙層電路板時,應為PCB內部的信號設計相對集成的接地層。在實際應用中,PCB接地阻抗受其形狀和信號線通孔,裂縫和開槽的影響。圖3a和3b分別顯示了不良和優秀的低阻抗接地平面設計。

開槽PCB對地阻抗的影響

在該圖中,所有組件都位于PCB的正面,而接地平面位于PCB的正面,芯片通過正面的印刷線ab連接,cd是背面的印刷線。在外部高頻共模干擾的壓力下,cd形成的開槽將導致印刷線回流的Z GND增加。Z GND在信號傳輸過程中波動,導致信號質量低。因此,cd之間的印刷線層可以在PCB布局設計過程中通過孔一遍又一遍地交換,使得Z GND會減少。

此外,兩個具有敏感信號的IC S可以排列在一起,使GND成為一個相對集成的接地平面,以確保信號在信號傳輸過程中不會受到干擾,注意通孔不能以很大的密度排列,否則會引起地平面裂紋,導致Z GND升級。

環測威檢測是一家專業解決產品電磁兼容問題的第三方檢測公司,提供全套EMC認證整改方案,相關產品測試可聯系工程師!

認證電話:4008-707-283

閱讀本文的人還閱讀了:

1、PCB設計過程中可能存在的問題及解決方案

2、PCB內部的串擾及其補救措施