PCB內部的電磁干擾EMI串擾及其補救措施

1、PCB印刷線和參考地之間的耦合

由于EMC主要討論高頻共模信號,因此PCB內外都無法避免分配參數。PCB和參考地之間發生電容耦合,其分布電容由極小空間內的極板電容和自然電容組成。板電容與PCB的大小成正比,與PCB和地之間的距離間接成比例。小空間內的自然電容與PCB內印刷線的等效直徑成正比。

因此,無論PCB放置在何處,即使在遠離地面的無限遠處,內部印刷線與地之間也始終存在分布電容,在PCB中,相對集成的GND平面到參考接地板的分布電容約為10pF,內部印刷線到參考接地板的分布電容大約在0.001pF到0.1pF或更低的范圍內。PCB中心印刷線的分布電容遠低于PCB邊緣印刷線的分布電容。

2、耦合在PCB內部

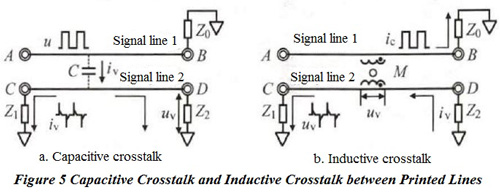

a、PCB內耦合理論及其對信號的影響,PCB內部的耦合由電容耦合和電感耦合組成,其理論如圖5所示。

印刷線之間的電容串擾和感應串擾

在該圖中,AB和CD都是平行印刷線,兩條線之間具有小的空間,Z 0表示信號線1的載波,而Z 1和Z 2分別表示信號線2的載波。在圖5a中,當印刷線AB上的信號峰值電壓為u時,信號上升時間為Δt,角度為頻率為ω,Z的電壓2將為u v = [Z 1 ? 2 /(Z 1 + Z 2)]Cδ ü /Δ 噸。雖然c具有非常低的值,但Δ的值ü / d 牛逼可以非常高,無法避免自己的產品。

在圖5b中,當AB上信號的峰值電流為I c時,信號上升時間為Δt,角頻率為ω,兩條印刷線之間的互感m將通過CD,其中感應電壓為u v = m ωi的?,雖然m的值很小,但信號頻率可能會增加。因此,他們的產品是無法避免的。

結果,電容耦合和電感耦合都與兩條印刷線的分布參數c或m有關,在PCB布局期間,可以通過增加平行線之間的距離來減小c和m的值。在實際電路中,電容耦合占據了大部分數字電路和PCB平面如果不平滑或存在開槽或裂縫,感應串擾將比電容串擾產生更大的影響。然而,當PCB的面積有限時,不能僅通過擴大平行線之間的距離來處理串擾。為了保持兩條相鄰平行線之間的小分布參數,應在投影區域中布置集成平面設計,并且好在頂部和底部具有接地層。

b、屏蔽地線減少電磁干擾EMI串擾的影響

串擾程度由許多元素決定,如信號頻率,信號上升沿時間,信號線之間的距離,驅動端口和接收端口的電特征以及PCB層數,通過在印刷線下設置集成接地層可以減少串擾,并且可以在信號之間添加屏蔽接地線。

在PCB布局過程中,兩個方面可以有利于阻止串擾,首先,應停止敏感的內部電路和外部電路。其次,應停止內部電路或噪聲電路與其他信號之間的串擾。在實際PCB布局中,應在PCB的同一層或不同層之間進行詳細測試,以檢測是否存在串擾風險。

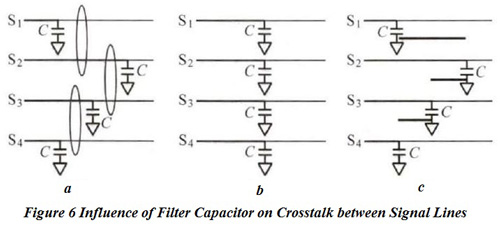

在PCB布局過程中,一些具有相同屬性的信號線應遵循相同時間和相同方向的密度路由,如果PCB空間的限制導致濾波器組件不能放置在同一條線上,則往往會引起信號之間的串擾。這種情況如下面的圖6所示。

濾波電容對信號線間串擾的影響

C、屏蔽地線對邊緣效應的影響

當具有高d u / d t,d i / d t的高靈敏度信號線或信號線沿著PCB邊緣布置時,它們將比布置在PCB中心的那些具有更大的EMC風險。邊緣信號線更容易通過較大的寄生電容接收高頻干擾或外部輻射。

在PCB面積的限制下,根據設計文件中的20H原理布置PCB非常困難。“分組”可用于減少干擾和外部輻射。分組線不需要滿足特定要求,例如厚度和形狀。通常當信號線太靠近PCB邊緣到銅板時,可以添加7到10密耳范圍內的地線作為屏蔽。

d、數字和模擬電路之間的相互干擾

當PCB保持高速數字電路和低電平模擬信號時,通常在PCB布局不良的情況下通過數字噪聲產生串行的串擾,數字和模擬電路之間的相互干擾是由以下原因引起的。首先,串擾噪聲是由寄生電容和寄生電感引起的,其次,功率紋波和數字芯片功率的不良去耦將導致功率噪聲。第三,接地阻抗和系統接地引起噪聲。噪聲問題應按電源,信號和接地順序處理。

以上是環測威總結關于PCB電磁兼容設計的一點經驗建議,環測威檢測是一家主要從事電磁兼容EMC測試的第三方檢測公司,有相關產品做EMC認證可咨詢工程師!

認證電話:4008-707-283

閱讀本文的人還閱讀了: