隨著信息技術的不斷發展,電子產品在功能,類別和結構方面變得越來越復雜,朝著多層方向和高密度方向推動PCB設計,因此,必須對PCB設計的EMC(電磁兼容性)給予很多關注,因為PCB的EMC設計不僅可以確保板上所有電路的正常和穩定工作,因此它們不會相互干擾,而是相互干擾。

還有效地減少了輻射傳輸和PCB的傳導發射,以阻止電路受到外部輻射和傳導的干擾,干擾是EMC重要的敵人,這篇文章會幫你解決電磁兼容問題。

PCB電磁干擾可分為三類:

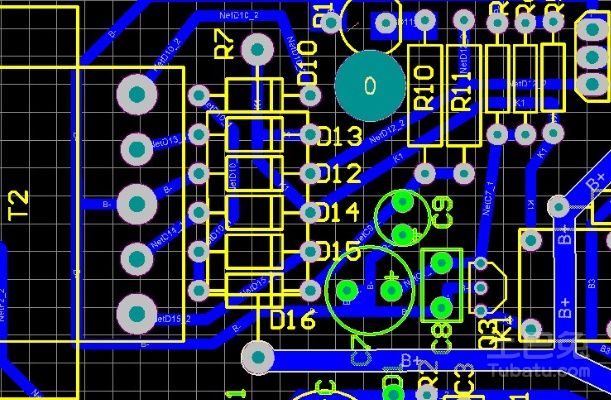

1)布局干擾是指由于PCB上不適當的元件放置而引起的干擾。

2)堆疊干擾是指由不科學的設置引起的噪聲干擾。

3)路由干擾是指PCB信號線,電源線和接地線之間距離設置不當,線寬或不科學的PCB布線方法造成的干擾。

在PCB干擾分類方面,可以從布局規則,堆疊策略和布線規則的角度分別采取一些抑制措施,減少甚至消除PCB干擾的影響,以確保與EMC設計標準的兼容性。

基于分類的PCB干擾相應抑制措施:

1、布局干擾的抑制措施

停止布局干擾的特權在于合理的PCB布局,應符合以下六條規則:

a、每個功能模塊的電路位置應根據信號電流位置合理設定,其流向應保持盡可能相同。

b、模塊電路中的核心部件應設置在中心位置,并且應盡可能縮短元件之間的引線,特別是高頻元件。

c、熱敏元件和芯片之間的集成應遠離加熱元件。

d、連接器位置應根據板上的元件位置確定。連接器應放置在PCB的一側,以阻止電纜從兩側引出,并減少共模(CM)電流輻射。

e、I / O驅動器應緊密靠近連接器,以阻止板上I / O信號的長距離路由。

f、熱敏元件不能彼此靠得太近,輸入和輸出元件也應遠離它們。

2、抑制堆疊干擾的措施

首先,PCB設計信息應該通過考慮的綜合元素來控制,包括信號線密度,功率和接地分類,以確定功率和確保實現電路功能的層數,堆疊策略的質量基本上與地平面或電源平面的瞬態電壓以及電源和信號的電磁屏蔽相關。

根據實際的堆疊設計經驗,堆疊設計應符合以下規則:

1)地平面和電源平面應相互鄰近,它們之間的距離應盡可能小。

2)信號平面應緊密靠近地平面或電源平面。單層或多層都可以。

在單層或雙層PCB設計過程中,應仔細設計電源線和信號線,為了減小電流的回路面積,接地線和電源線應緊密相互靠近,并保持相互平行。對于單層PCB,應在重要信號線的兩側設置保護接地線。一方面,它旨在縮小信號的環路面積。另一方面,可以避免信號線之間的串擾。

對于雙層PCB,也可以設置保護接地線,或者在重要信號的圖像平面上實現大面積接地。盡管PCB制造和裝配調試簡單方便,但直接模擬復雜的PCB(如數字電路和數字模擬電路)是不可接受的,因為輻射會隨著沒有參考平面的環路面積的增加而增加。

如果成本足夠,建議使用多層PCB,在多層PCB設計過程中必須遵循三條規則:

1)對于重要的信號線,例如具有強輻射的總線或時鐘線以及具有高靈敏度的線路,應在兩個接地平面之間或緊靠接地平面的信號平面上實現布線,這有利于信號環路區域收縮,輻射強度降低和抗干擾強化。

2)應確保邊緣輻射得到有效控制。與相鄰的接地層相比,電源面應在內部減小5至20H(H表示電介質厚度)。

3)如果底層和頂層之間存在高頻信號線,則應將它們布置在頂層和地平面之間,以防止高頻信號線輻射到空間。

3、路由干擾的抑制措施為了禁止干擾,在路由方面必須遵守以下規則:

1)輸出端子和輸入端子的引線應避免長距離并聯。通過增加接地線或增加線之間的距離可以減少并聯串擾。

2)路由寬度永遠不會突然改變。角應為弧形或天使度為135°。

3)隨著環路面積,電流和信號頻率的增加(減小),載流環路的外部輻射增加(減少),因此當電流流過時必須減小引線環路面積。

4)應增加引線長度,同時增加寬度,以降低引線的阻抗。

5)為了大限度地降低相鄰線路之間的噪聲耦合和串擾,請在線路之間進行隔離處理,以確保布線隔離。

6)應設置分流隔離鍵信號,并通過保護電路保護鍵信號。

此外,當路由信號線,電源線和接地線時,請遵循路由規則,根據自身的特點和功能:

a、公共接地線應布置在PCB邊緣,網狀或環形; 接地線應盡可能厚,并應涂上更多的銅箔,以加強屏蔽效果; 模擬接地應采用數字接地隔離,單點并聯應應用于模擬地的低頻接地。多點串聯應適用于高頻地。在實際路由中,串聯連接可以與并聯連接組合。

b、應盡可能增加電源線的寬度,并應減小回路電阻,以確保接地線和電源線的方向與數據傳輸方向之間的同步。對于多層PCB,應減少電源線與地平面或電源平面之間的距離。應該獨立地為每個功能單元供電,并且由公共電源供電的電路應該彼此接近并且相互兼容。

C、信號線應盡可能短,以確保減少干擾信號耦合路徑,時鐘信號線和敏感信號線應首先布線,然后是高速信號線,后是無關緊要的信號線。如果信號線彼此不兼容,則應實施隔離處理以停止產生耦合干擾,關鍵信號路由不能超過由焊盤和通孔過孔引起的分離區域或甚至參考平面空間。否則,信號回路區域將增加,同時,為了禁止邊緣輻射,鍵信號線和參考平面之間的距離不能小于3H(H指的是鍵信號線和參考平面之間的高度)。

我們唯一要擔心的是害怕不成功,對于電子工程師來說,在PCB設計過程中,干擾總是讓你煩惱。但是,只要我們知道干擾源自何處并采取有效措施,絕對會在完全實現PCB性能的情況下降低干擾。

環測威檢測科技是一家專業解決電磁兼容EMC認證問題的第三方檢測機構,總部位于沙井新橋,有相關產品EMC測試可咨詢工程師!

認證電話:4008-707-283

閱讀本文的人還閱讀了:

1、高速PCB布線技術,以減少電磁干擾EMI的影響2、單層PCB,雙層PCB和多層PCB方面的電磁兼容性EMC設計