問:為什么ESD目標級工業委員會提倡使用類似SPICE的電路模擬來評估系統級的ESD可靠性?

答:這是一種省時的選擇,可以先找出ESD資格測試時出現的問題,然后通過低效的試錯程序來糾正這些問題。利用電路仿真對系統ESD可靠性進行虛擬樣機設計,稱為系統高效ESD設計,或SEED。

問:系統級ESD模擬的障礙是什么?

答:微電子元器件供應商一般不提供其零部件的ESD型號。

問:有沒有提出解決辦法?

答:有人認為,經驗模型可以適用于TLP(傳輸線脈沖)I-V測量數據[1]。

問:這些經驗模型是如何分類的?

答:大多數是分段線性模型。還研究了更先進的非線性模型,如遞歸神經網絡。

為了模擬系統級ESD,必須模擬沿放電路徑的所有微電子元件;這些元件可能包括瞬態電壓抑制器、鐵氧體扼流圈或其他離散元件。本文主要研究集成電路元件。如果以合理的精度模擬集成電路引腳處的靜電感應電壓和電流波形,就可以檢查該部件是否會被驅動到其安全工作區域之外,還是會發生熱故障。這種分析足以確定集成電路在ESD資格測試中是否會避免硬故障。

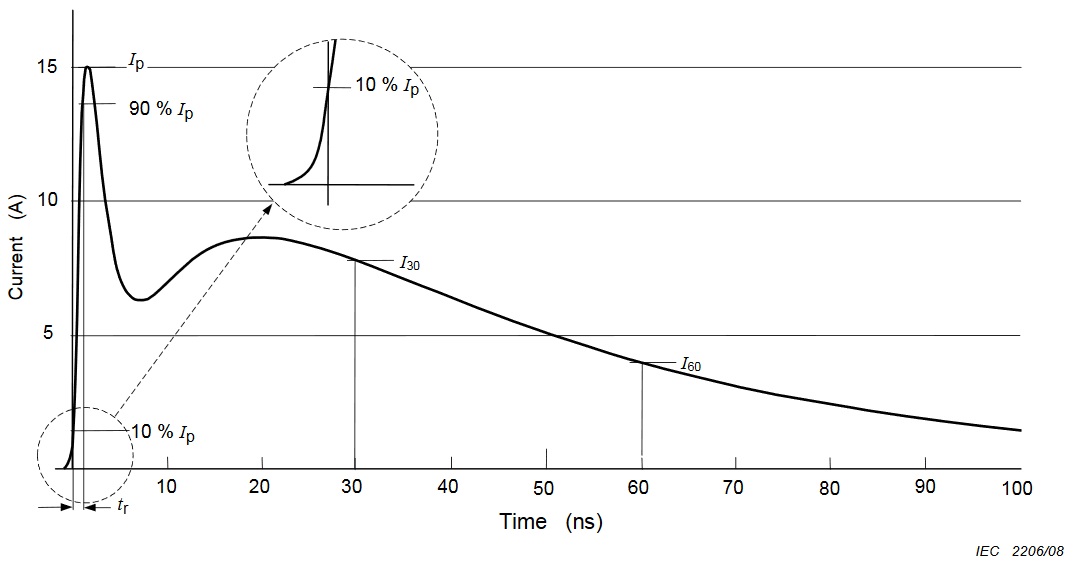

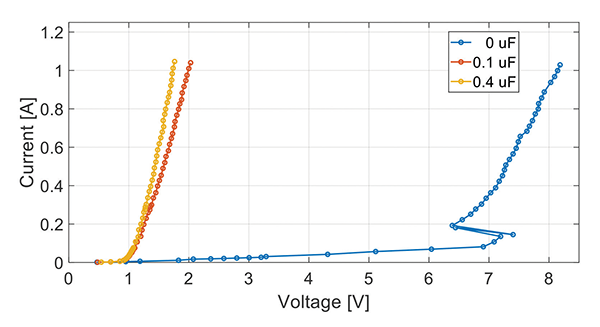

元件對ESD的響應通常用傳輸線脈沖(TLP)測試來評估。脈沖I-V曲線應在電源和電源狀態下測量,這就要求被測試的設備,即IC,安裝在帶有電源的測試板上。參考文獻,包含一個測試板設計示例。通常,脈沖I-V曲線適合于分段線性模型.生成的模型是靜態模型,因為I-V曲線不能提供被測設備的動態響應信息。

如果集成電路的瞬態響應是線性的,那么在原則上,靜態模型可以用S參數測量得到的瞬態模型來擴展。在許多情況下,集成電路的瞬態靜電放電響應主要由封裝的寄生電感和電容元件控制。在這種情況下,可能不需要做任何測量來獲得瞬態模型,因為許多IC供應商提供的IBIS模型包括對包的描述。從TLP測量得到的分段線性模型和RLC封裝模型可以連接在一起,形成一個完整的ESD組件模型[7],如圖1所示。

一個由靜態I-V模型和封裝模型組成的組件模型很好地預測了集成電路對tlp測試儀產生的方型電流脈沖的瞬態響應,但不是全部。這一發現表明,片上半導體器件的動態非線性響應并不總是被封裝阻抗的動態響應所掩蓋。

在測量數據的基礎上建立芯片對靜電放電動態響應的精確模型,即封裝的集成電路對ESD型電流脈沖的瞬態響應是非常困難的,部分原因是當集成電路安裝在電路板上時,無法精確地將探針放置在IC輸入端。IC設計人員可以更容易地創建組件ESD模型。

設計者的模型將包括芯片Netlist,以及設備的緊湊模型;例如,IC供應商不愿意向他們的客戶提供這類模型,因為這些模型可能會披露知識產權(IP)。準確的瞬態模型能否被重新表示為IP模糊行為模型是值得考慮的問題。其中一個候選模型是遞歸神經網絡。

遞歸神經網絡(RNN)是非線性狀態空間系統的一種通用逼近器,這類系統由常微分方程描述。RNN特別適合處理時間序列數據,例如實驗室儀器或電路模擬器提供的數據。IC IO引腳的RNN模型

輸入,u,可以是電流或電壓,以及輸出,y是另一個量,即電壓或電流。WrWuWy , bu 和by是模型參數。x 表示系統的內部狀態。例如,如果被建模的系統是單個二極管,則變量映射可能是電壓為u,存儲電荷x,以及當前的y。實際上,用戶沒有指定從物理量到RNN模型內部狀態的映射;相反,內部狀態是從數據中“學習”出來的,不需要與可識別的物理量相對應。圖2提供了RNN的圖像視圖。

RNN模型可以在Verilog-A中實現,然后使用ADS、HSPICE和譜等商用電路模擬器進行仿真。

為了說明瞬態行為建模的可行性,通過對全芯片ESD保護網絡的Netlist進行仿真,生成訓練數據。利用這些數據,利用開源優化軟件建立了電路的RNN模型.圖3顯示了使用電路的Netlist描述和RNN模型獲得的仿真結果。與行為模型相關的誤差很小,小于3%。應該注意的是,在圖3的模擬中應用于電路的刺激沒有包括在訓練數據中。重要的是要證明一個行為模型是可概括的,也就是說,它預測正確的行為對以前看不見的刺激作出反應。

stimuli

雖然瞬態行為模型的好處是顯而易見的,但是需要做更多的工作來確定RNN是否是最適合表示組件的ESD響應的模型。雖然RNN被認為是一個“通用”模型,但它存在一些困難,例如,必須確保所學習的網絡對于所有輸入刺激都是穩定的。

TLP提供了一個單端口的I-V測量,因此從TLP測量數據中提取的模型是一個單端口模型。需要注意的是,在IC引腳處測量到的脈沖I-V曲線不僅描述了IC,而且還描述了IC和板級電流路徑的綜合效應。流入IC的IO引腳的電流按受板級電力傳輸網絡(PDN)的阻抗影響的比例在可能的返回路徑之間劃分。

因此,如圖4所示,在IC引腳上測量的I-V特性受板PDN阻抗的影響。如果用組件的多端口ESD模型代替現在使用的單端口模型,則可以在仿真中捕捉到系統電路板的全部效果。即使PDN阻抗太低,板對被測I-V的影響也是可以忽略的,軟失效分析可能需要一個多端口的集成電路模型。

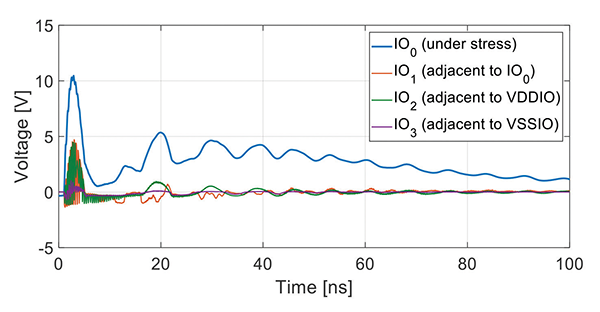

在資格測試中,大約一半的系統級ESD故障是軟故障。其中許多故障是由于IO引腳上出現的噪音(“小故障”)造成的,這是連接線或封裝痕跡之間磁耦合的結果[12]。時域電磁模擬器可以進行噪聲耦合分析.假設ESD電流主要以信號引腳進入IC;片上保護網絡將ESD電流分流回封裝(然后是板)。

因此,芯片上的電路決定了封裝鍵合線或軌跡的組合構成了返回路徑,而封裝級的噪聲耦合模擬應該能夠理解芯片的效果。EM模擬器不能提供這樣的功能,但是可以使用混合電磁電路模擬器.在[13]中,Speed 2000模擬器被用來模擬ESD誘導的噪聲耦合到集成電路封裝內的信號線上;示例結果如圖5所示。

在過去的5到6年中,工業界和大學的研究人員已經在系統級ESD模擬方面取得了最新進展,本文對其中的一些活動進行了概述。要建立可重復和準確的方法來描述組件對系統級ESD的響應,并就最合適的模型結構達成共識,還有許多工作要做。