與軟件系統的發展相比,電子硬件設計及其優化已經出現了長時間消耗和高成本等實際問題。在實際設計中,工程師傾向于更多地關注高度原則性的問題,但是導致對印刷電路板操作的巨大影響只是一些我們必須反復糾正的詳細錯誤。完美生成PCB是不可能的,但可以逐步優化,本文將首先列出電路設計,PCB生產和維護方面的一些問題,然后提供一些易于使用的方法,以有限的成本優化定制PCB。

多通道功率整流LED的耐壓保護

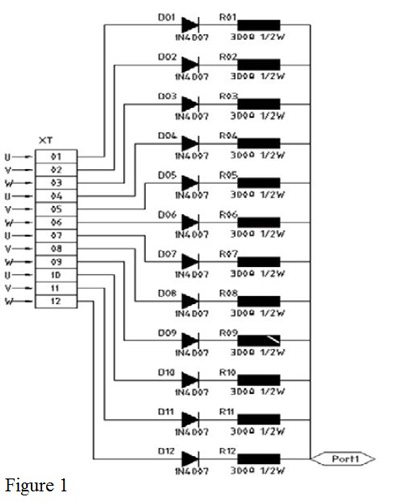

以走廊公共電力設備為例,為了保證電路的正常工作,利用多通道電源為AC-DC模塊的電源模塊供電,參數“Uin = AC85~264V”。采用300Ω1/ 2W碳電阻串聯的IN4007整流LED用于多路輸入隔離。圖1是該產品的電路圖。

IN4007整流LED電路圖

從理論上講,這是一個完美的想法,而實際使用中存在嚴重問題,在沒有考慮尖峰電壓的情況下,在正常情況下,多通道電源之間的電壓可以達到AC400V,IN4007的耐壓可以達到1000V。正確的組件被拿起來,對嗎?但事實是由于耐壓問題經常發生短路爆炸,導致整個產品報廢。當然,低質量的元件和LED的老化也會導致問題,但即使安裝了具有更高耐壓的高質量LED或LED而不是之前的那些,問題仍然存在。

考慮到保修期內早期疲勞的質量問題和吞吐量(TPY)的存在,組件幾乎不可能達到100%TPY,對于該電路,該先進電路需要24個整流LED,廢品率范圍為2.4%至7.2%。具有這種品質的PCB永遠無法完全滿足客戶的需求,事實上,這是一種易于使用的方法來處理這個問題。只要在每個循環中再放置一個IN4007系列,就可以輕松解決這個問題,因為此時,電路電壓降低了0.7V,對輸出沒有影響。只需稍微增加成本就可以產生雙耐壓值,并將誤差發生率降低到0.5%。

小型繼電器頻繁運行解決電磁干擾EMI問題

由于電弧放電時小型繼電器在PCB上產生的電磁干擾會在切斷高電流時產生,干擾不僅影響CPU的正常運行,導致頻繁的復位,而且使解碼器和驅動器產生錯誤的信號和指令,導致組件實現的錯誤。所有這些影響都會導致有缺陷的貨物和事故。為了解決這個問題,可以考慮兩個方面:增加CPU的抗干擾能力和減少干擾源。

1.增加CPU的抗干擾能力。必須安裝具有高抗干擾能力的CPU,CPU的選擇也需要實驗和測試,例如90C52RC SCM是理想的選擇,這種類型的CPU具有20KV的抗靜電能力和4KV抗快速脈沖和電磁能力。

2.減少干擾源

a、繼電器驅動放大器能夠有效降低線圈停電時反電動勢產生的干擾。

b、RC吸收電路并聯在繼電器觸點之間,可以快速吸收噪聲干擾。

c、電路板采用銅包覆。銅包層有助于減少繼電器干擾。

d、必須仔細選擇繼電器。具有相同規格的繼電器始終具有不同線圈功率的選擇。基本原理是線圈功率越大,繼電器觸點開關動作越快,觸點間電弧放電時間越短,電磁干擾時間越短。

墊子的改進

當PCB處于維護狀態時,無法避免拆卸或焊接,當元件從PCB上拆卸下來時,老化的PCB或PCB太小的焊盤總會看到焊盤脫落并且板孔壁上的焊接層脫落。

1.關于針墊關閉,可以使用短線連接同一路徑上的附近焊盤,該短線可根據距離和可容納的電流量進行選擇。對于短距離,修整后的廢棄引腳或引腳頭可用于焊接; 對于長距離,可以使用具有外部絕緣層的銅線進行連接,以避免由線路和其他部件的引腳之間的連接引起的短路。當在這個地方總是發生焊盤問題時,可以驗證這里的PCB設計是如此不合理,以至于必須優化焊盤的設計。可在可用空間內將墊片設計成長圓形或水滴形狀,并且可以添加短而粗的銅包層線以增加其對PCB材料的吸收能力。

2.對于板孔壁上的焊接層,原因在于板孔尺寸小,當元件從PCB上拆卸下來時,會出現板孔壁的焊接層。因此,建議在設計過程中,墊孔的尺寸應比引腳的尺寸大0.3至0.5mm,當焊盤孔壁上的焊錫層脫落時,可以嘗試這種方法。在涂錫之前,應先安裝新元件的引腳,使焊錫層稍厚一些,接下來是引腳焊接,引腳上的焊錫層能夠輕松焊接PCB上的焊盤。

更換易受攻擊的組件

只要使用電子元件,某些部件就會變得脆弱,需要更換或更換,維護這些部件的常用方法是通過焊接,這會導致大量時間消耗,從而極大地影響工作效率。建議將堿基添加到易受攻擊的組件中,或者可以通過插頭或插入行進行連接。這種方法可以幫助工程師節省大量的時間和精力。

PCB設計和優化是一個復雜的過程,需要設計藍圖和細節,優化每個細節會導致PCB制造過程中的時間消耗和成本降低。PCB設計需要考慮的問題有很多,滿足電磁兼容測試的要求是設計師必須重視的一環,產品通過EMC認證才能順利走向市場,相關PCB電磁兼容測試問題可咨詢環測威檢測工程師!

認證電話:4008-707-283

閱讀本文的人還閱讀了:

1、怎么確保PCB電磁兼容EMC設計的首次成功2、傳導發射測試DC-DC轉換器噪聲評估