在EMC設計中,電容是應用廣泛的元件之一,主要用于構成各種低通濾波器或用作去耦電容和旁路電容。大量實踐表明:在EMC設計中,恰當選擇與使用電容,不僅可解決許多EMI問題,而且能充分體現效果良好、價格低廉、使用方便的優點。若電容的選擇或使用當,則可能根本達不到預期的目的,甚至會加刷EMT程度。

本文根據EMC設計原理和不同結構電容的特點,結合相關研究的新進展,針對電容在EMC設計中的一些不恰當的認識與做法,討論了電容在EMC設計中的應用技巧,對EIC設計具有指導作用。

1、濾波器結構的選擇

EMC設計中的濾波器通常指由1,C構成的低通泌波器。不同結構的濾波器的主要區別之一,是其中的電容與電感的聯接方式不同。濾波器的有效性不僅與其結構有關,而且還與連接的網絡的阻抗有關。如單個電容的濾波器在高阻抗電路中效果很好,而在低阻抗電路中效果很差。

傳統上,在濾波器兩端的端接阻抗為50歐姆的條件下描述濾波器的特性(這一點往往未被注意),因為這樣測試方便,并且是符合射頻標準的。

但是,實踐中源阻抗Zs和負載阻抗Zi很復雜,并且在要抑制的頻率點上可能是未知的。如果濾波器的一端或兩端與電抗性元件相聯結,則可能會產生諧振,使某些頻率點的插入損耗變為插入增益。

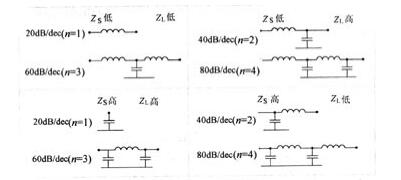

可見,正確選擇濾波器的鉆構至關重要。究竟是選擇電容、電感還是兩者的組合,是由所謂的”大不匹配原則“決定的。簡言之,在任何濾波器中,電容兩端存在高阻抗,電感兩端存在低阻抗。圖1是利用大不匹配原則得到的濾波器的結構與Z5和ZL.的配合關系。每種情形給出了2種結構及相應的衰減斜率(n表示濾波器中電容元件和電感元件的總數)。

濾波器的結構與Zs和Z.的配合關系

但是,如何判定2,和乙的值是高或低,一些資料上并未作具體說明[1,2],實踐中也往往不清楚。

Zs和1.的所謂的高值或低值的臨界選取有一定的隨機性,選取50n作為邊界值是比較合適的。順便指出,在電子電路中,因信號一般較弱,而RC低通濾波器對信號有一定的衰減,故很少使用。

2、自諧振頻率與載止須率

2.1去相電容的自諧振頻率

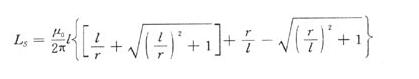

實際的電容都有寄生電感Ls,Ls的大小基本上取決于引線的長度,對圓形、導線類型的引線,上’的典型值為10mH/cm[3]。典型的陶瓷電容的引線約有6mm長,會引入約15mll的電感””,引線電感也可由下式估算[4]:

其中:/和r分別為引線的長度和半徑。

寄生電感會與電容產生串聯諧振,即自諧振,在自諧振頻率fo處,去耦電容呈現的阻抗小,去耦效果好。

但對須率f高于f/o的噪聲成份,去耦電容呈電感性,阻抗隨頻率的升高而變大,使去耦或旁路作用大大下降。實踐中,應根據噪聲的高頻率faax 來選擇去根電容的自諧振頻率f0,佳取值為fo=fmmx。

但是,一些資料上只是從電容的寄生電感的角度給出了自諾舔頻率fo的資料。實際上,去根電容的自諧振頻率不僅與電容的寄生電感有關,而且還與過孔的寄生電感[5]、聯結去耦電容與芯片電源正負極引腳的印制導線的寄生電感[6.7]等都有關系。如果不注意這一點,查得的資料或自己的估算往往與實際情況相去甚遠。

實踐中,一般是先確定去耦電容的鉆構(電容的寄生電感與其鉆構關系密切),再用試驗的方法確定容量。

2.2電源濾波器的釣自諧振頻率

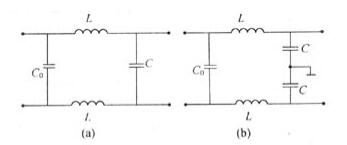

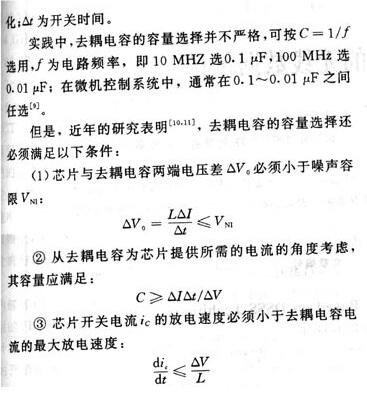

在交流電源進線與電源變壓器之間設置電測濾波器是抗EMI的常用措施之一。常用的電源濾波器如圖2所示。人們一般對去耦電容的自諧振須率問題比較注意,實際上電源濾波器也有自諧振頻率問題,處理不當,同樣達不到預期的目的。

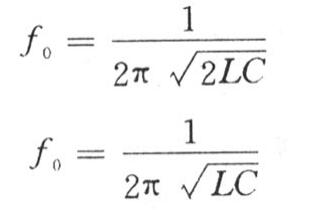

對圖2所示的濾波器,分析可知,當電感的電阻rL很小時,自諧振頻率分別為:

自諧振頻率(圖)

設計電源濾波器時,必須使濾波器的自諧振頻率遠小于噪聲頻率。處理不當,不僅不能衰減噪聲,反而會放大確聲。

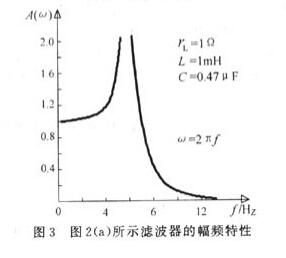

例如[8]圖2(a)所示的濾波器,如果取1=lalH,rl.=l歌婷,C=0.47uF(這也是許多資料上推薦的參數),可算出f0=5.2kHz。而EMC測試中的快速脈沖群頻率為5.0klHz(2kV)或2.5kHz(4kY),5.0kHz剛好諧據,2.5kHz也不會被衰誠,如圖3所示。這說明濾波器中元件參數選取不當,可能根本起不到提高EWC性能的作用。

圖2:電源濾波器

3、電容結構的選擇

從理論上講.電容的容量越大,容抗就越小,濾波效果就越好。一些人也有這種習慣認識。但是,容量大的電容一般寄生電感也大,自諧振須率低(如典型的陶瓷電容,0.1uF的fo=5MHz,0.0lulF的fo=15Mlz,0.00luF的fO=50MHz),對高頻噪聲的去耦效果差,甚至根本起不到去耦作用。分立元件的濾波器在頻辛超過10MHz時,將開始失去性能。元件的物理尺寸越大,轉折點頻幸越低。這些問恩可以過選擇特殊結構的電容來解決。

貼片電容的寄生電惑幾乎為零,總的電夠也可以減小到元件本身的電感、通常只是傳統電容寄生電感的1/3~1/5,自諧振須率可達同樣容量的帶引線電容的2倍(也有資料說可達l0倍),是射頻應用的理想選擇。傳統上,射頻應用一般選擇瓷片電容。但在實踐中,超小型聚脂或聚苯乙烯薄膜電容也是適用的,因為他們的尺寸與瓷片電容相當。

三端電容能將小瓷片電容頻率范圍從50Hz以下拓展到200Mlz以上,這對抑制VHF頻段的噪聲是很有用的。要在VMIF或更高的頻段獲得更好的濾波效果,特別是保護屏蔽體不被穿透,必須使用饋通電容。

4、電容容量的選擇

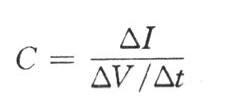

在數字系統中,去耦電容的容量通常按下式估算:

其中:/x1為瞬變電流;AN為邏輯器件允許的電源電壓變

此外。當電源引線比較長時,瞬變電流會引起較大的壓降,此時就要加容納電容以維持器件要求的電壓值。

5、去根電容的安裝方式與PCB設計

安裝去耦電容時,一般都知道使電容的引線盡可能短。但是,實踐中往往受到安裝條件的限劍,電容的引線不可能取得很短。況且,電容引線的寄生電感只是影響目諧振須率的因素之一,自諾振頻率還與過孔的寄生電感、相關印制導線的寄生電感等因素有關。一味地追求引線短,不僅困難。而且根本達不到目的。

這說明要保證去耦效果,在PCB設計時,就要考慮相關問題。設計印制導線時,應使去耦電容距離芯片電源正負樓引廁盡可能近(當然電容引線要盡可能短)。設計過孔時應盡量減小過孔的寄生電感。

6、結語

人們不斷糾正或放棄電容在EWC設計中的一些傳統認識與做法。電容在EC設計中的作用大小與多種因素有關,已其中的很多因素一直在不斷的研究與變化中。所以,要充分發揮電容在EC設計中的作用,及時了解相關研究的新進展,及時采用新技術,是非常重要的。

環測威檢測是一家從事電磁兼容emc測試、FCC認證、無線產品認證的第三方檢測公司,相關產品測試問題可在線咨詢工程師!

免費電話:4008-707-283

閱讀本文的人還閱讀了:

1、電磁兼容測試項目有哪些?

2、emc設計的技巧:避免電磁兼容測試失敗的有效方法